AMD从小型CPU转向小型GPU

在高性能计算应用中,对突破性性能的追求从未停止过,特别是在人工智能,机器学习和大数据分析等新兴应用提出了更高的性能要求之后。但是,过程突破的速度逐渐放慢,每个过程节点带来的频率红利逐渐变小。

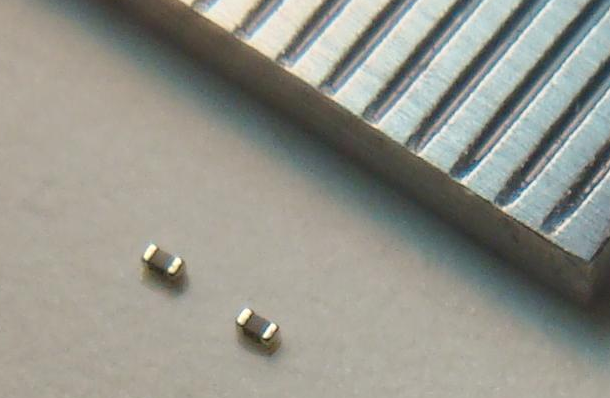

为了降低生产和开发成本并提高产量,许多CPU制造商开始将目光投向小型芯片。 2020年的最后一天,AMD宣布了自己在小型芯片GPU上的专利,这引起了很多热烈讨论。

每个人都在猜测,小芯片是否可以成为后摩尔时代芯片设计创新的强大工具? AMD:从小型CPU到小型GPU,AMD从很早就开始致力于小型芯片的开发。无论是EPYC服务器CPU还是线程撕裂器台式机CPU,小型芯片设计都已被广泛使用。

在AMD看来,传统的单芯片处理器将一个或多个CPU内核放在单个裸片上,以加快时钟频率和缓存读取。尽管此策略对于需要大量CPU使用的作业非常合理,但是仍然存在局限性。

小芯片设计可以带来更快的架构创新,尤其是在数据中心等应用中。在去年的ISSCC2020上,AMD强调了第二代EPYC服务器CPU上小型芯片的优势。

在具有Zen2架构的EPYC服务器CPU上,AMD在CPU内核上使用TSMC的Foundry 7nm小芯片,而IOD仍在使用GlobalFoundries的14nm工艺。 AMD提到该设计可实现更多的内核数量和更高的性能,并显着降低了成本。

AMD最近宣布的小芯片GPU专利也引起了很多热潮。该专利展示了一种使用高带宽交叉链接的小型芯片GPU设计方案。

Chiplet GPU / AMD在此专利中,AMD提到,由于大多数应用程序都是在单个GPU的前提下编写的,因此,为了保留现有的应用程序编程模型,在GPU上实现芯片设计一直是一件大事。挑战。

该专利使用总线将第一个GPU小芯片连接到CPU,其余的GPU通过被动交叉链接连接。如今,许多架构至少具有在GPU芯片上一致分布的第一级缓存,例如L3或其他最后一级缓存(LLC)。

在这种设计中,这些物理资源被放置在不同的芯片上,并且提供了通信连接以确保高速缓存的一致性。在工作过程中,内存地址请求从CPU发送到GPU小芯片,后者与高带宽无源交叉链接进行通信以定位所需的数据。

因此,从CPU的角度来看,它仍然在单独的GPU上解决。 。

英特尔:使用小型芯片创建客户2.0芯片客户2.0解决方案/英特尔的设计还为英特尔提供了更多的芯片定位自由度。例如,游戏玩家需要更高的图形性能,而开发人员则更渴望更高的计算能力。

强大的AI性能。这是英特尔构想的客户2.0愿景,旨在通过智能感知为消费者带来无缝的高性能体验。

尽管GPU一直是英特尔的弱点之一,但这并不意味着英特尔在显示领域没有做出任何努力。自从Intel从AMD图形部门挖走首席架构师Raja Koduri之后,Intel就开始致力于离散图形。

英特尔在2019年底发布了一款超级计算级GPU,代号为PonteVecchio。 GPU基于7纳米工艺和小芯片技术,并将于2021年作为图形加速器安装在Aurora超级计算机上。

小型芯片的支持:没有创新的互连和封装技术的新型互连和封装技术,小型芯片设计也将无法实现获得立足点。关于小芯片的包装,英特尔已经计划了详细的包装路线图。

处理器封装路线图/英特尔在KabyLakeG处理器和AgilexFPGA上,英特尔实现了EMIB的2.5D封装方法。英特尔在Lakefield系列处理器上使用的Foveros3D封装技术是对EMIB的进一步补充。

该技术可以将凸块高度进一步降低到50-25um,并实现接近1000IO / mm2的密度。 Infinity架构/ AMD,但是如果您希望在分解后保持小芯片的连接性,那么互连技术就非常有用,例如AMD在Zen架构CPU中引入的InfinityFabric。

AMD将InfinityFabric视为连接主要产品线的基石。通过第三代Infinity框架,AMD能够在CPU和GPU之间提供大带宽和低延迟的连接以及统一的内存访问,从而改善AMD产品的综合性能并简化。

为了降低生产和开发成本并提高产量,许多CPU制造商开始将目光投向小型芯片。 2020年的最后一天,AMD宣布了自己在小型芯片GPU上的专利,这引起了很多热烈讨论。

每个人都在猜测,小芯片是否可以成为后摩尔时代芯片设计创新的强大工具? AMD:从小型CPU到小型GPU,AMD从很早就开始致力于小型芯片的开发。无论是EPYC服务器CPU还是线程撕裂器台式机CPU,小型芯片设计都已被广泛使用。

在AMD看来,传统的单芯片处理器将一个或多个CPU内核放在单个裸片上,以加快时钟频率和缓存读取。尽管此策略对于需要大量CPU使用的作业非常合理,但是仍然存在局限性。

小芯片设计可以带来更快的架构创新,尤其是在数据中心等应用中。在去年的ISSCC2020上,AMD强调了第二代EPYC服务器CPU上小型芯片的优势。

在具有Zen2架构的EPYC服务器CPU上,AMD在CPU内核上使用TSMC的Foundry 7nm小芯片,而IOD仍在使用GlobalFoundries的14nm工艺。 AMD提到该设计可实现更多的内核数量和更高的性能,并显着降低了成本。

AMD最近宣布的小芯片GPU专利也引起了很多热潮。该专利展示了一种使用高带宽交叉链接的小型芯片GPU设计方案。

Chiplet GPU / AMD在此专利中,AMD提到,由于大多数应用程序都是在单个GPU的前提下编写的,因此,为了保留现有的应用程序编程模型,在GPU上实现芯片设计一直是一件大事。挑战。

该专利使用总线将第一个GPU小芯片连接到CPU,其余的GPU通过被动交叉链接连接。如今,许多架构至少具有在GPU芯片上一致分布的第一级缓存,例如L3或其他最后一级缓存(LLC)。

在这种设计中,这些物理资源被放置在不同的芯片上,并且提供了通信连接以确保高速缓存的一致性。在工作过程中,内存地址请求从CPU发送到GPU小芯片,后者与高带宽无源交叉链接进行通信以定位所需的数据。

因此,从CPU的角度来看,它仍然在单独的GPU上解决。 。

英特尔:使用小型芯片创建客户2.0芯片客户2.0解决方案/英特尔的设计还为英特尔提供了更多的芯片定位自由度。例如,游戏玩家需要更高的图形性能,而开发人员则更渴望更高的计算能力。

强大的AI性能。这是英特尔构想的客户2.0愿景,旨在通过智能感知为消费者带来无缝的高性能体验。

尽管GPU一直是英特尔的弱点之一,但这并不意味着英特尔在显示领域没有做出任何努力。自从Intel从AMD图形部门挖走首席架构师Raja Koduri之后,Intel就开始致力于离散图形。

英特尔在2019年底发布了一款超级计算级GPU,代号为PonteVecchio。 GPU基于7纳米工艺和小芯片技术,并将于2021年作为图形加速器安装在Aurora超级计算机上。

小型芯片的支持:没有创新的互连和封装技术的新型互连和封装技术,小型芯片设计也将无法实现获得立足点。关于小芯片的包装,英特尔已经计划了详细的包装路线图。

处理器封装路线图/英特尔在KabyLakeG处理器和AgilexFPGA上,英特尔实现了EMIB的2.5D封装方法。英特尔在Lakefield系列处理器上使用的Foveros3D封装技术是对EMIB的进一步补充。

该技术可以将凸块高度进一步降低到50-25um,并实现接近1000IO / mm2的密度。 Infinity架构/ AMD,但是如果您希望在分解后保持小芯片的连接性,那么互连技术就非常有用,例如AMD在Zen架构CPU中引入的InfinityFabric。

AMD将InfinityFabric视为连接主要产品线的基石。通过第三代Infinity框架,AMD能够在CPU和GPU之间提供大带宽和低延迟的连接以及统一的内存访问,从而改善AMD产品的综合性能并简化。

- 电话:0755-29796190

- 陈经理 17727576190 QQ:2330223425 Email:xiao@jepsun.com

- 陆经理 18038104190 QQ:2065372476 Email:tao@jepsun.com

- 李经理 13316946190 QQ:2057469664 Email:ys@jepsun.com

- 聂经理 18923485199 QQ:2215069954 Email:momo@jepsun.com

- 地址:深圳市宝安区翻身路富源大厦1栋7楼

-